### Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1110 Microprocessor

**Developer's Manual**

June 2000

**Notice:** This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local Intel sales office that you have the latest technical information before finalizing a design.

Order Number: 278240-003

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

This document is an intermediate draft for comment only and is subject to change without notice. Readers should not design products based on this document.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1110 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2000

\*Other brands and names are the property of their respective owners.

| 1 | Introduction1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1         |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

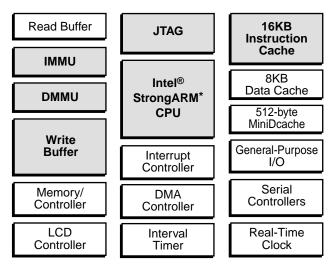

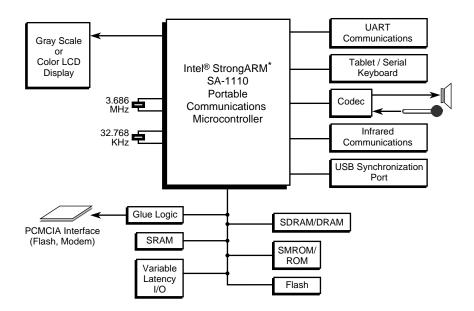

|   | 1.1       Intel® StrongARM SA-1110 Microprocessor       1         1.2       Overview       1         1.3       Example System       1         1.4       ARM Architecture       1         1.4.1       26-Bit Mode       1         1.4.2       Coprocessors       1         1.4.3       Memory Management       1         1.4.4       Instruction Cache       1         1.4.5       Data Cache       1         1.4.6       Write Buffer       1         1.4.7       Read Buffer       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 456666677 |

| 2 | Functional Description2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

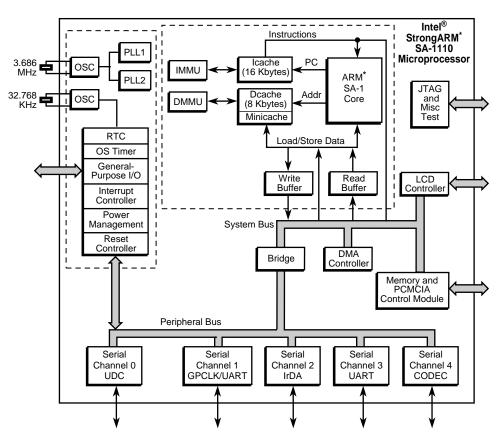

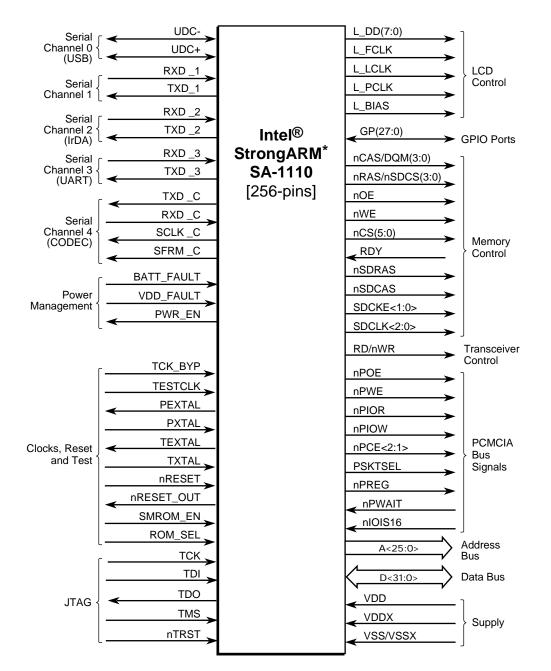

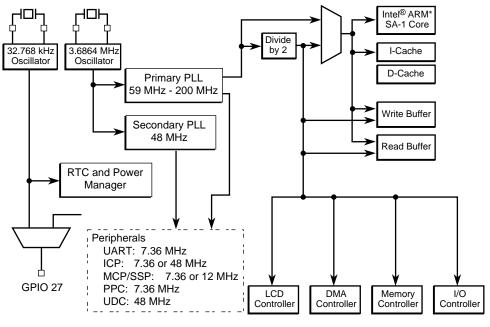

|   | <ul> <li>2.1 Block Diagram</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|   | 2.3 Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4         |

|   | 2.4 Memory Map2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 3 | ARM Implementation Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|   | <ul> <li>3.1 Big and Little Endian</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|   | 3.2.1 Power-Up Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2         |

|   | 3.2.2 ROM Size Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|   | 3.2.3 Abort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|   | 3.2.5 Exception Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4         |

|   | 3.2.6 Interrupt Latencies and Enable Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| 4 | Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

| - | 4.1 Instruction Set4–                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|   | 4.2 Instruction Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| 5 | Coprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1         |

|   | 5.1 Internal Coprocessor Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|   | 5.2       Coprocessor 15 Definition         5.2.1       Register 0 – ID         5.2.1       Second Sec |           |

|   | 5.2.1 Register 0 – 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|   | 5.2.3 Register 2 – Translation Table Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

|   | 5.2.4       Register 3 – Domain Access Control         5.2.5       Register 4 – RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

|   | 5.2.6 Register 5 – Fault Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

|   | 5.2.7 Register 6 – Fault Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

|   | 5.2.8       Register 7 – Cache Control Operations         5.2.9       Register 8 – TLB Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|   | 5.2.10 Register 9 – Read-Buffer Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

| 5.2.11 Registers 10 – 12 RESERVED                                                    | 5–7 |

|--------------------------------------------------------------------------------------|-----|

| 5.2.12 Register 13 – Process ID Virtual Address Mapping                              |     |

| 5.2.13 Register 14 – Debug Support (Breakpoints)                                     | 5–7 |

| 5.2.14 Register 15 – Test, Clock, and Idle Control                                   | 5–9 |

| Caches, Write Buffer, and Read Buffer                                                | 6–1 |

| 6.1 Instruction Cache (Icache)                                                       |     |

| 6.1.1 Icache Operation                                                               |     |

| 6.1.2 Icache Validity                                                                |     |

| 6.1.2.1 Software Icache Flush                                                        |     |

| 6.1.3 Icache Enable/Disable and Reset                                                | 6–2 |

| 6.1.3.1 Enabling the Icache                                                          |     |

| 6.1.3.2 Disabling the Icache                                                         |     |

| 6.2 Data Caches (Dcaches)                                                            |     |

| 6.2.1 Cacheable Bit – C                                                              |     |

| 6.2.1.1 Cacheable Reads $-C = 1$                                                     |     |

| 6.2.1.2 Noncacheable Reads – $C = 0$                                                 |     |

| 6.2.2 Bufferable Bit – B                                                             |     |

| 6.2.3 Software Dcache Flush                                                          |     |

| 6.2.3.1 Doubly Mapped Space                                                          |     |

| 6.2.4 Dcaches Enable/Disable and Reset<br>6.2.4.1 Enabling the Dcaches               |     |

| <ul><li>6.2.4.1 Enabling the Dcaches</li><li>6.2.4.2 Disabling the Dcaches</li></ul> |     |

| 6.3 Write Buffer (WB)                                                                |     |

| 6.3.1 Bufferable Bit                                                                 |     |

| 6.3.2 Write Buffer Operation                                                         |     |

| 6.3.2.1 Writes to a Bufferable and Cacheable Location (B=1,C=1)                      |     |

| 6.3.2.2 Writes to a Bufferable and Noncacheable Location (B=1,C=0)                   |     |

| 6.3.2.3 Unbufferable Writes (B=0)                                                    |     |

| 6.3.3 Enabling the Write Buffer                                                      |     |

| 6.3.3.1 Disabling the Write Buffer                                                   |     |

| 6.4 Read Buffer (RB)                                                                 | 6–6 |

| Memory Management Unit (MMU)                                                         | 7–1 |

| 7.1 Overview                                                                         |     |

| 7.1.1 MMU Registers                                                                  |     |

| 7.2 MMU Faults and CPU Aborts                                                        |     |

| 7.3 Data Aborts                                                                      |     |

| 7.3.1 Cacheable Reads (Linefetches)                                                  |     |

| 7.3.2 Buffered Writes                                                                |     |

| 7.4 Interaction of the MMU, Icache, Dcache, and Write Buffer                         |     |

| 7.5 Mini Data Cache                                                                  |     |

| Clocks                                                                               | 8–1 |

| 8.1 Intel® StrongARM SA-1110 Crystal Oscillators                                     |     |

| 8.2 Core Clock Configuration Register                                                |     |

| 8.2.1 Restrictions on Changing the Core Clock Configuration                          |     |

| 8.3 Driving Intel® StrongARM SA-1110 Crystal Pins from an External Source            |     |

| 8.4 Clocking During Test                                                             |     |

|                                                                                      |     |

9

| System Control Module                                                                                                | 9–1  |

|----------------------------------------------------------------------------------------------------------------------|------|

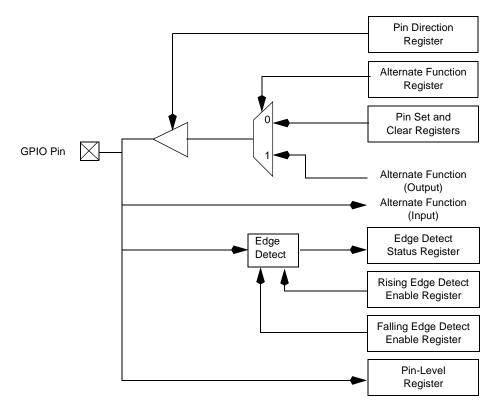

| 9.1 General-Purpose I/O                                                                                              | 9–1  |

| 9.1.1 GPIO Register Definitions                                                                                      |      |

| 9.1.1.1 GPIO Pin-Level Register (GPLR)                                                                               |      |

| 9.1.1.2 GPIO Pin Direction Register (GPDR)                                                                           |      |

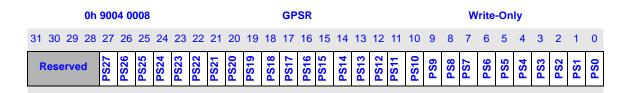

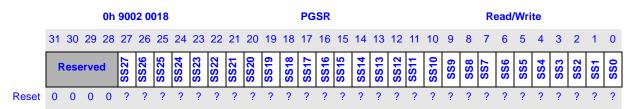

| 9.1.1.3 GPIO Pin Output Set Register (GPSR) and Pin Output                                                           |      |

| Clear Register (GPCR)                                                                                                | 9–5  |

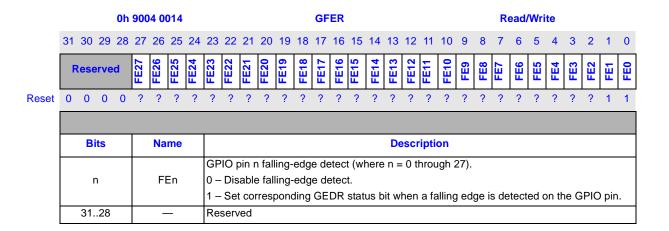

| 9.1.1.4 GPIO Rising-Edge Detect Register (GRER) and                                                                  |      |

| Falling-Edge Detect Register (GFER)                                                                                  |      |

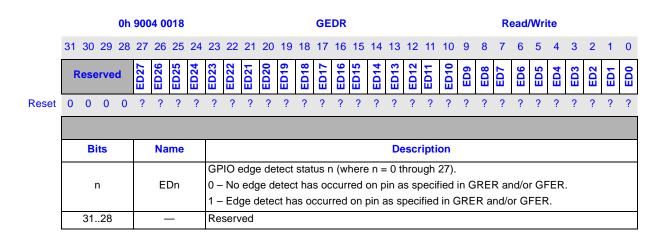

| 9.1.1.5 GPIO Edge Detect Status Register (GEDR)                                                                      |      |

| 9.1.1.6 GPIO Alternate Function Register (GAFR)                                                                      |      |

| 9.1.2 GPIO Alternate Functions.                                                                                      |      |

| 9.1.2.1 3.6864 MHz Option for GP 27 Alternate Output Function                                                        |      |

| 9.1.3 GPIO Register Locations                                                                                        |      |

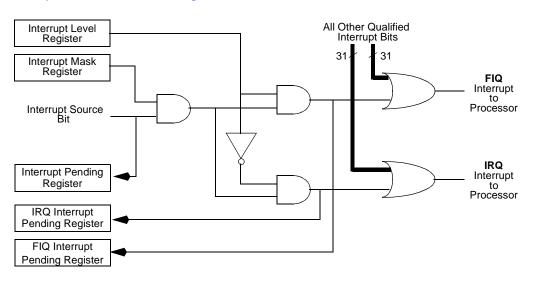

| 9.2 Interrupt Controller                                                                                             |      |

| 9.2.1 Interrupt Controller Register Definitions                                                                      | 9-12 |

| 9.2.1.1 Interrupt Controller Pending Register (ICPR)<br>9.2.1.2 Interrupt Controller IRQ Pending Register (ICIP) and | 9–12 |

| 9.2.1.2 Interrupt Controller IRQ Pending Register (ICIP) and<br>FIQ Pending Register (ICFP)                          | 0 1/ |

| 9.2.1.3 Interrupt Controller Mask Register (ICMR)                                                                    | 0_15 |

| 9.2.1.4 Interrupt Controller Level Register (ICLR)                                                                   |      |

| 9.2.1.5 Interrupt Controller Control Register (ICCR)                                                                 | 9–17 |

| 9.2.2 Interrupt Controller Register Locations                                                                        |      |

| 9.3 Real-Time Clock                                                                                                  |      |

| 9.3.1 RTC Counter Register (RCNR)                                                                                    |      |

| 9.3.2 RTC Alarm Register (RTAR)                                                                                      |      |

| 9.3.3 RTC Status Register (RTSR)                                                                                     |      |

| 9.3.4 RTC Trim Register (RTTR)                                                                                       |      |

| 9.3.5 Trim Procedure                                                                                                 |      |

| 9.3.5.1 Oscillator Frequency Calibration                                                                             |      |

| 9.3.5.2 RTTR Value Calculations                                                                                      |      |

| 9.3.6 Real-Time Clock Register Locations                                                                             | 9–22 |

| 9.4 Operating System Timer                                                                                           |      |

| 9.4.1 OS Timer Count Register (OSCR)                                                                                 |      |

| 9.4.2 OS Timer Match Registers 0-3 (OSMR 0, OSMR 1, OSMR 2, OSMR 3).                                                 |      |

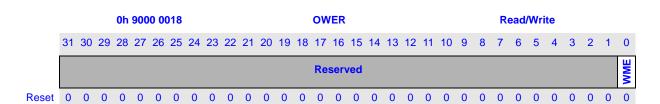

| 9.4.3 OS Timer Watchdog Match Enable Register (OWER)                                                                 |      |

| 9.4.4 OS Timer Status Register (OSSR)                                                                                |      |

| 9.4.5 OS Timer Interrupt Enable Register (OIER)                                                                      |      |

| 9.4.6 Watchdog Timer                                                                                                 |      |

| 9.4.7 OS Timer Register Locations                                                                                    |      |

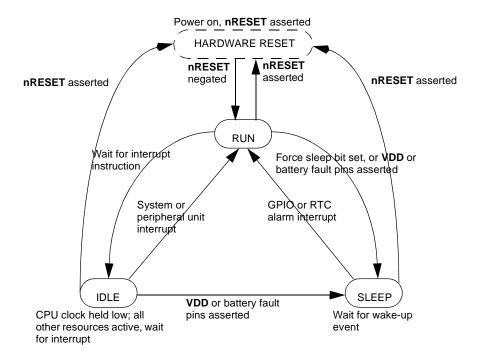

| 9.5 Power Manager                                                                                                    |      |

| 9.5.1 Run Mode                                                                                                       |      |

| 9.5.2 Idle Mode                                                                                                      |      |

| 9.5.2.1 Entering Idle Mode                                                                                           |      |

| 9.5.2.2 Exiting Idle Mode                                                                                            |      |

| 9.5.3 Sleep Mode                                                                                                     |      |

| 9.5.3.1 CPU Preparation for Sleep Mode                                                                               |      |

| 9.5.3.2 Events Causing Entry into Sleep Mode                                                                         | 9–28 |

| 9.5.3.3 The Sleep Shutdown Sequence                                                                                  | 9–28 |

| 9.5.3.4 During Sleep Mode                                                                                            |      |

| 9.5.3.5 The Sleep Wake-Up Sequence                                                                                   | 9–29 |

| 9.5.3.6    | Booting After Sleep Mode                                           |       |

|------------|--------------------------------------------------------------------|-------|

| 9.5.3.7    | 5                                                                  |       |

|            | otes on Power Supply Sequencing                                    |       |

|            | ssumed Behavior of an Intel® StrongARM SA-1110 /stem in Sleep Mode | 0_31  |

|            | n Operation in Sleep Mode                                          |       |

|            | ower Manager Registers                                             |       |

| 9.5.7.1    | Power Manager Control Register (PMCR)                              |       |

| 9.5.7.2    | Power Manager General Configuration Register (PCFR)                |       |

| 9.5.7.3    | Power Manager PLL Configuration Register (PPCR)                    |       |

| 9.5.7.4    | Power Manager Wake-Up Enable Register (PWER)                       |       |

| 9.5.7.5    | Power Manager Sleep Status Register (PSSR)                         |       |

| 9.5.7.6    | Power Manager Scratch Pad Register (PSPR)                          |       |

| 9.5.7.7    | Power Manager GPIO Sleep State Register (PGSR)                     | 9–40  |

| 9.5.7.8    | Power Manager Oscillator Status Register (POSR)                    |       |

|            | ower Manager Register Locations                                    |       |

|            | et Controller                                                      |       |

|            | eset Controller Registers                                          |       |

| 9.6.1.1    | Reset Controller Software Reset Register (RSRR)                    |       |

| 9.6.1.2    |                                                                    |       |

| 9.6.2 Re   | eset Controller Register Locations                                 | 9–44  |

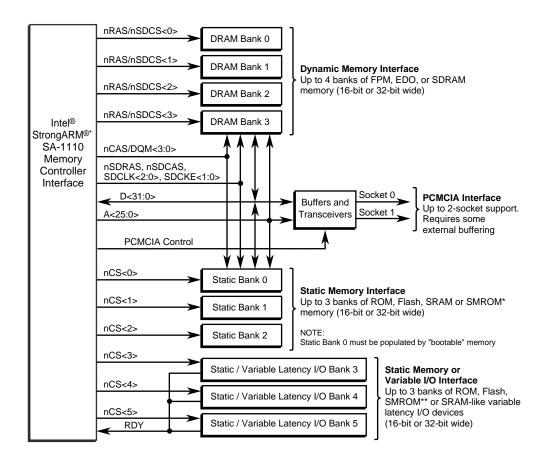

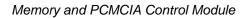

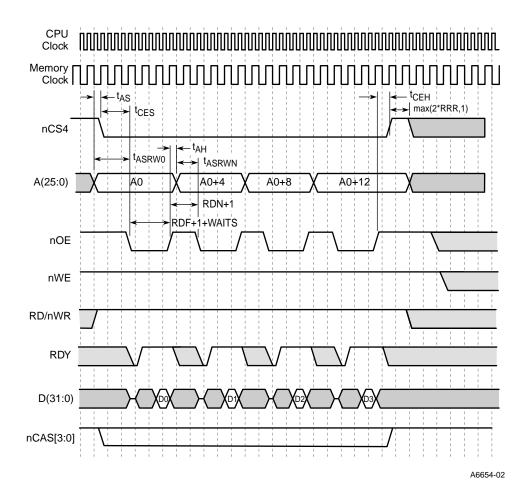

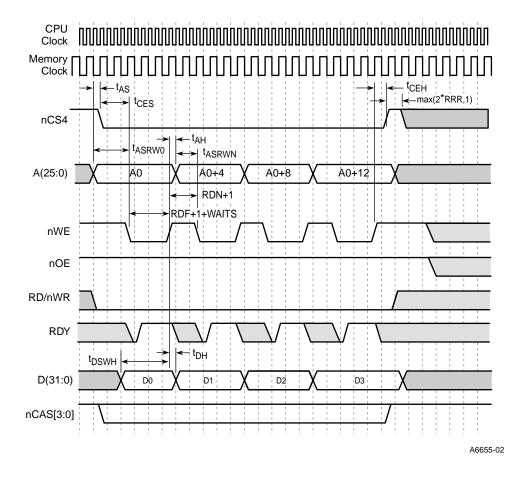

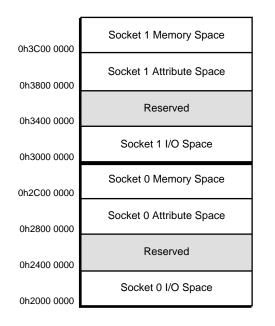

| Memory and | d PCMCIA Control Module                                            | 10–1  |

| 10.1 Ove   | rview of Operation                                                 |       |

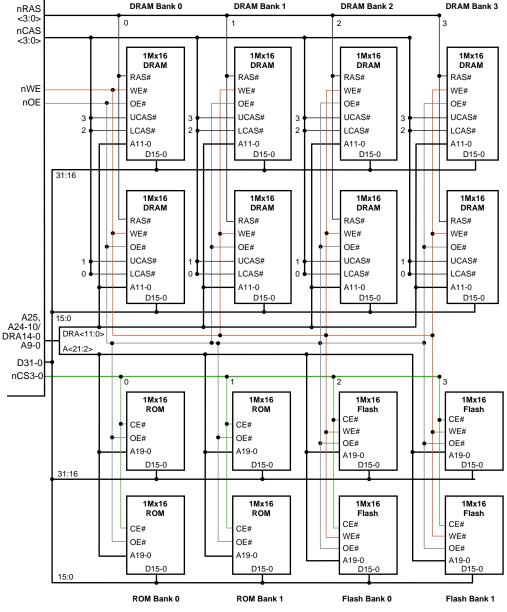

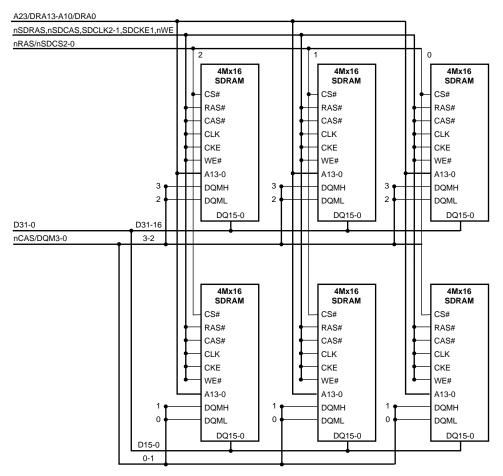

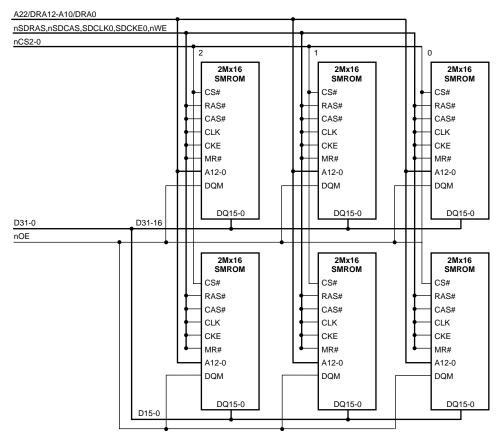

|            | emory System Examples                                              |       |

|            | pes of Memory Accesses                                             |       |

|            | eads                                                               |       |

| 10.1.4 W   | /rites                                                             |       |

| 10.1.5 T   | ransaction Summary                                                 |       |

| 10.1.6 Re  | ead-Lock-Write                                                     |       |

| 10.1.7 A   | borts and Nonexistent Memory                                       |       |

| 10.2 Mer   | nory Configuration Registers.                                      |       |

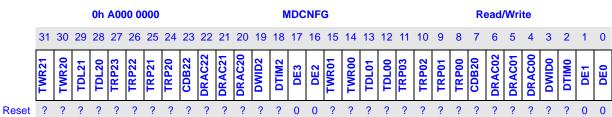

| 10.2.1 DF  | RAM Configuration Register (MDCNFG)                                |       |

| 10.2.2 DF  | RAM Refresh Control Register (MDREFR)                              | 10–14 |

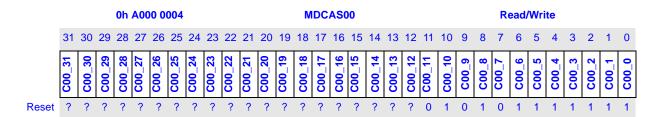

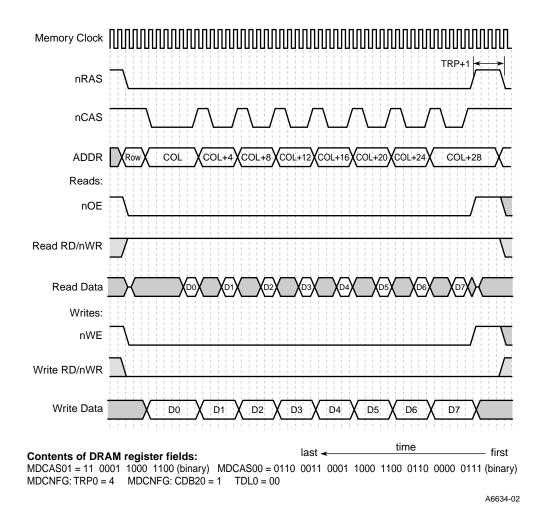

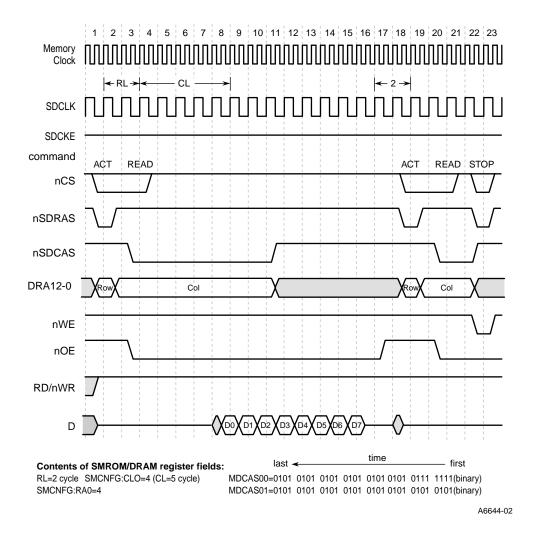

| 10.2.3 C/  | AS Waveform Rotate Registers (MDCAS00, MDCAS01, MDCA               | AS02, |

| M          | DCAS20, MDCAS21, MDCAS22)                                          |       |

| 10.2.3.1   |                                                                    |       |

|            | MDCAS Registers with SDRAM and SMROM                               |       |

|            | atic Memory Control Registers (MSC2 – 0)                           |       |

|            | pansion Memory (PCMCIA) Configuration Register (MECR)              |       |

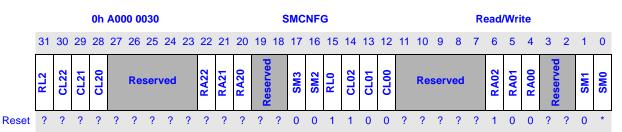

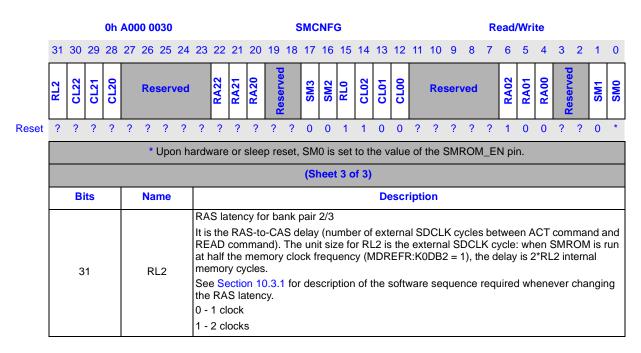

|            | COM Configuration Register (SMCNFG)                                |       |

|            | nanging SMROM RAS Latency                                          |       |

|            | amic Interface Operation                                           |       |

|            | RAM Overview                                                       |       |

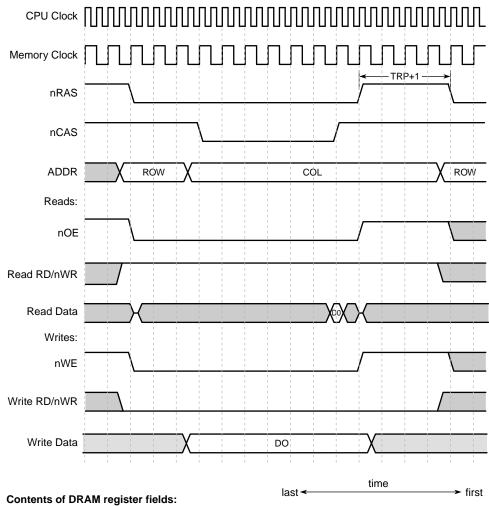

|            | RAM Timing                                                         |       |

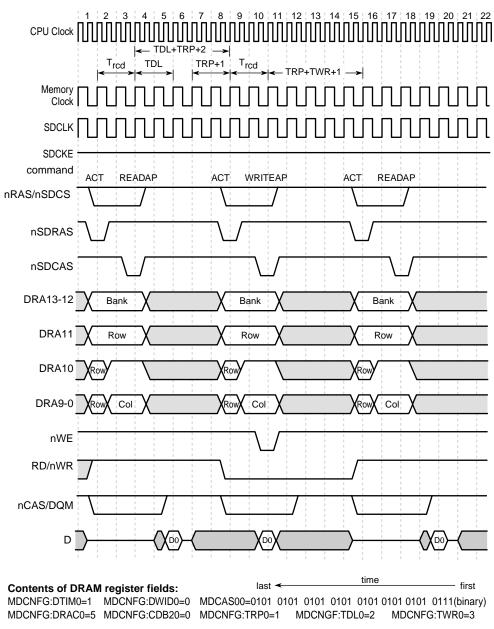

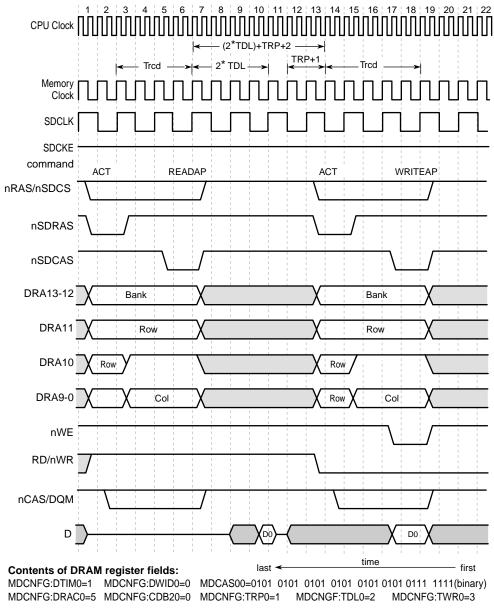

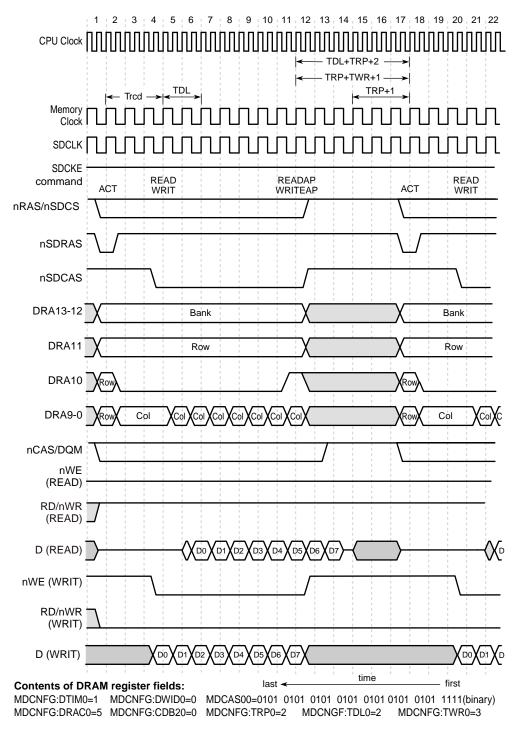

|            | DRAM Overview                                                      |       |

|            | DRAM Commands                                                      |       |

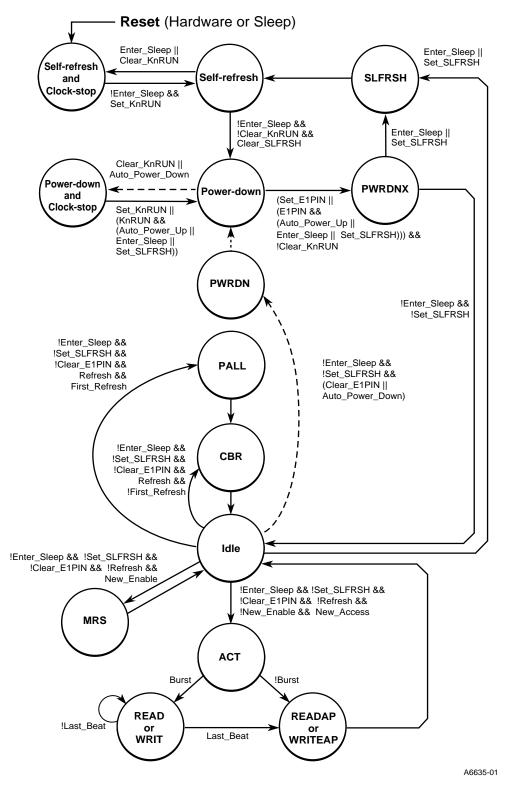

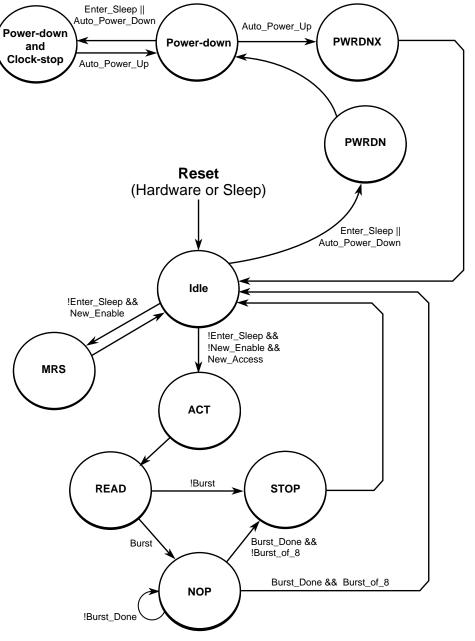

|            | DRAM State Machine                                                 |       |

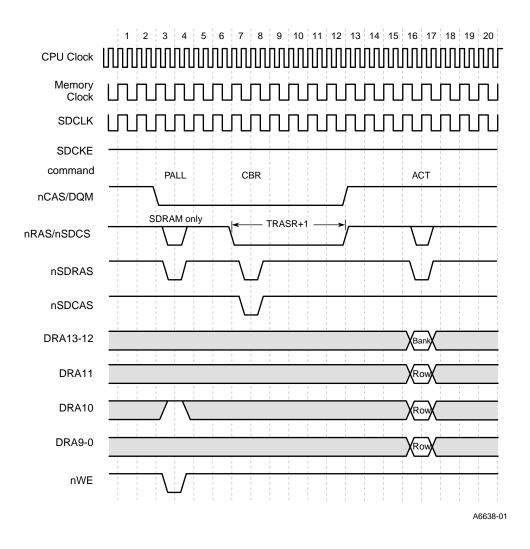

|            | RAM/SDRAM Refresh                                                  |       |

|            | RAM/SDRAM Self-Refresh in Sleep Mode                               |       |

| 10.5 Stati | c Memory Interface                                                 | 10–42 |

10

### int<sub>el</sub>

11

|              | OM Interface Overview                                                      |       |

|--------------|----------------------------------------------------------------------------|-------|

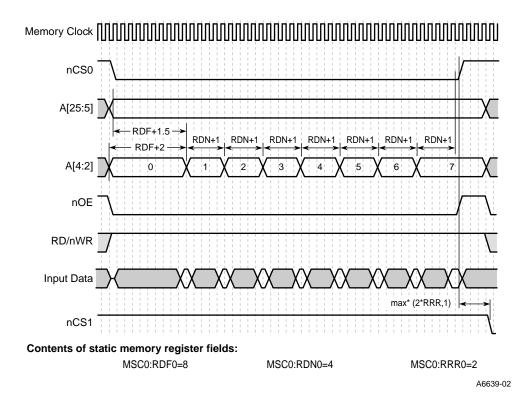

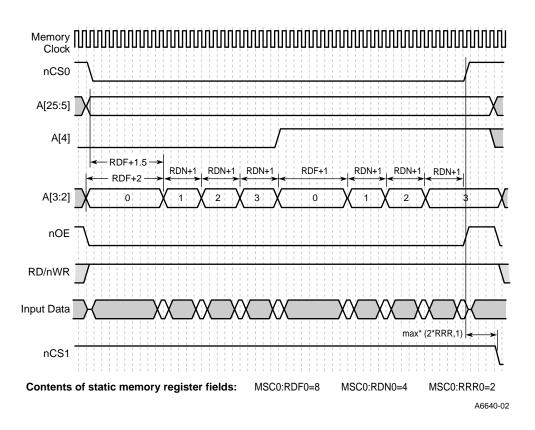

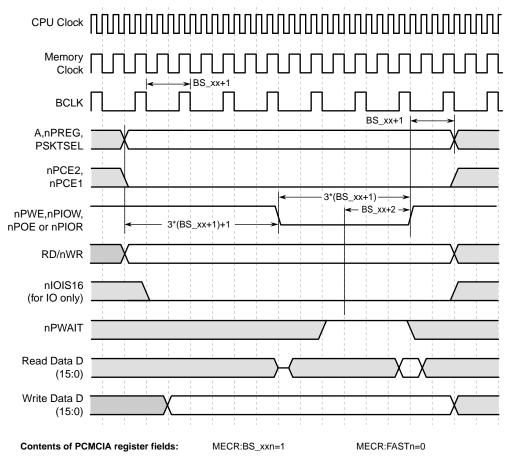

| 10.5.2 RC    | OM Timing Diagrams and Parameters                                          | 10–43 |

|              | RAM Interface Overview                                                     |       |

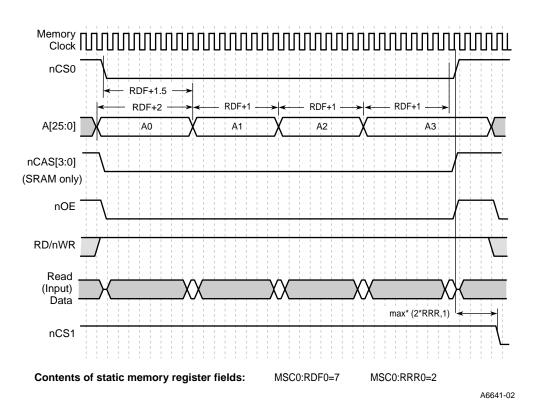

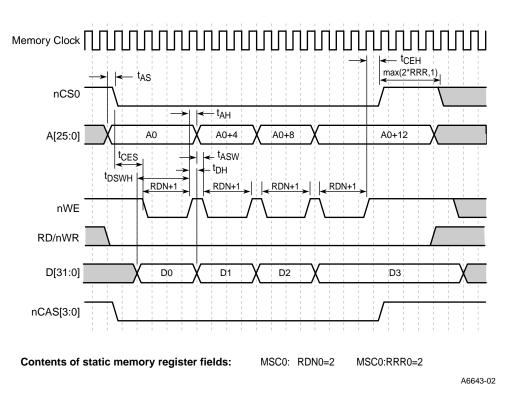

| 10.5.4 SF    | RAM Timing Diagrams and Parameters                                         |       |

| 10.5.5 Va    | ariable Latency I/O Interface Overview                                     |       |

| 10.5.6 Va    | ariable Latency I/O Timing Diagrams and Parameters                         |       |

| 10.5.7 FL    | ASH Memory Interface Overview                                              |       |

|              | LASH Memory Timing Diagrams and Parameters                                 |       |

|              | MROM Overview                                                              |       |

|              | MROM Commands                                                              |       |

|              | MROM State Machine                                                         |       |

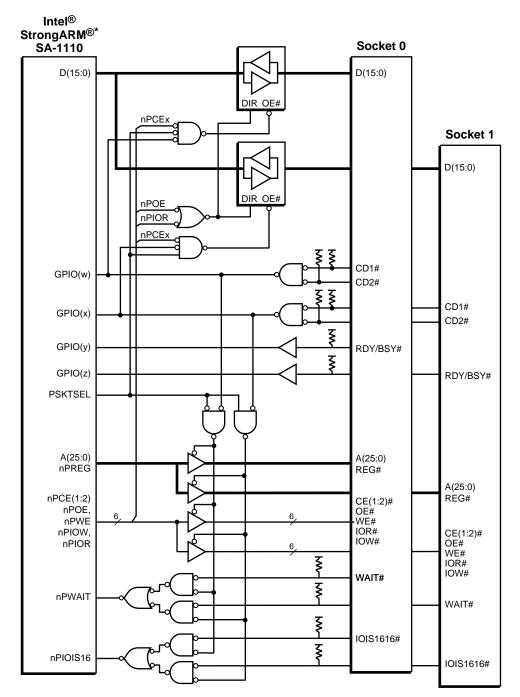

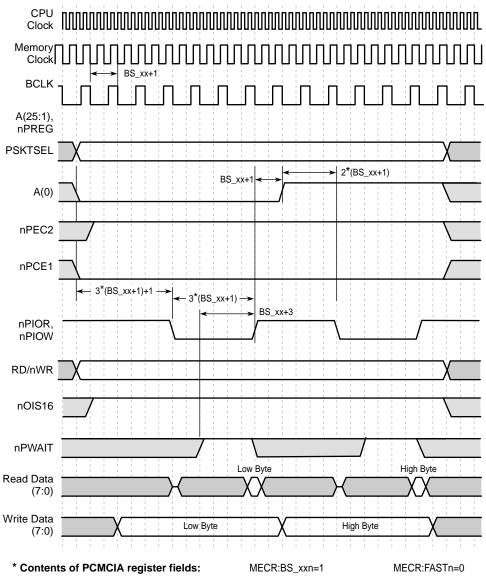

|              | ICIA Overview                                                              |       |

|              | 2-Bit Data Bus Operation                                                   |       |

|              | External Logic for PCMCIA Implementation                                   |       |

|              | CMCIA Interface Timing Diagrams and Parameters                             |       |

|              | nory Interface Reset and Initialization                                    |       |

|              | ardware or Sleep Reset Procedures                                          |       |

|              | oftware or Watchdog Reset Procedures                                       |       |

|              | nate Memory Bus Master Mode                                                |       |

|              | -                                                                          |       |

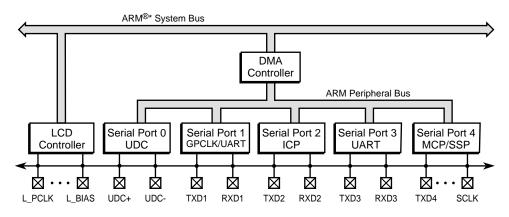

| Peripheral C | Control Module                                                             | 11–1  |

| 11.1 Read    | d/Write Interface                                                          |       |

|              | nory Organization                                                          |       |

|              | rupts                                                                      |       |

|              | bheral Pins                                                                |       |

|              | of the GPIO Pins for Alternate Functions                                   |       |

|              | Controller                                                                 |       |

|              | MA Register Definitions                                                    |       |

|              |                                                                            |       |

|              | DMA Device Address Register (DDARn)<br>DMA Control/Status Register (DCSRn) |       |

|              | DMA Buffer A Start Address Register (DBSAn)                                |       |

|              | DMA Buffer A Transfer Count Register (DBSAII)                              |       |

| 11.0.1.4     | DMA Buffer B Start Address Register (DBSBn)                                |       |

| 11.0.1.3     | DMA Buffer B Transfer Count Register (DB3BII)                              |       |

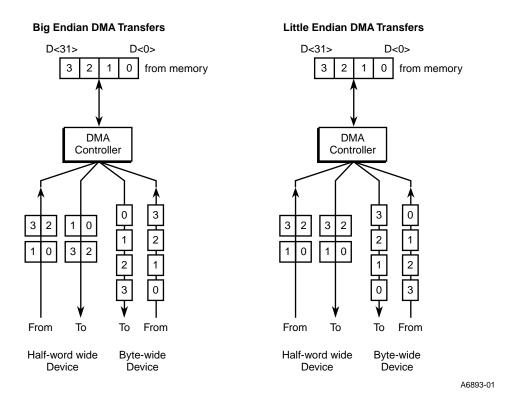

|              | MA Operation                                                               |       |

|              | MA Operation                                                               |       |

|              | •                                                                          |       |

|              | Controller                                                                 |       |

|              | CD Controller Operation                                                    |       |

|              | DMA to Memory Interface                                                    |       |

|              | Frame Buffer                                                               |       |

|              | Input FIFO<br>Lookup Palette                                               |       |

| 11.7.1.4     | •                                                                          |       |

| 11.7.1.6     |                                                                            |       |

|              | LCD Controller Pins                                                        | 11–23 |

|              | CD Controller Register Definitions                                         |       |

|              | 5                                                                          |       |

|              | CD Controller Control Register 0                                           |       |

| 11.7.3.1     | LCD Enable (LEN)                                                           |       |

|              | Color/Monochrome Select (CMS)                                              |       |

| 11.7.3.3     | Single-/Dual-Panel Select (SDS)<br>LCD Disable Done Interrupt Mask (LDM)   |       |

| 11.7.3.4     |                                                                            |       |

| 11.7.3.5 Base Address Update Interrupt Mask (BAM)                        |      |     |    |

|--------------------------------------------------------------------------|------|-----|----|

| 11.7.3.6 Error Interrupt Mask (ERM)                                      | . 11 | 1-: | 28 |

| 11.7.3.7 Passive/Active Display Select (PAS)                             | . 11 | 1-: | 28 |

| 11.7.3.8 Big/Little Endian Select (BLE)                                  |      |     |    |

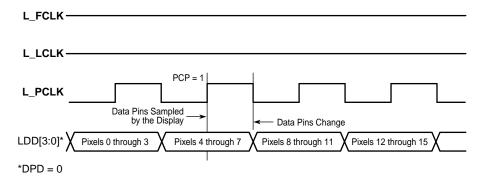

| 11.7.3.9 Double-Pixel Data (DPD) Pin Mode                                |      |     |    |

| 11.7.3.10 Palette DMA Request Delay (PDD)                                |      |     |    |

| 11.7.4 LCD Controller Control Register 1                                 |      |     |    |

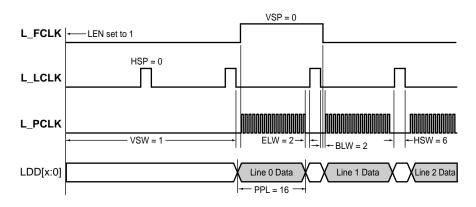

| 11.7.4.1 Pixels Per Line (PPL)                                           | . 11 | 1–: | 33 |

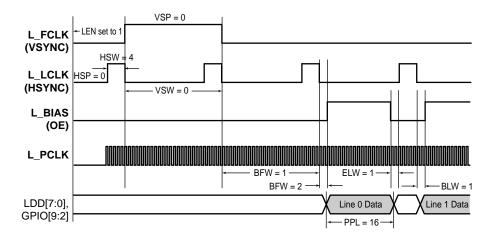

| 11.7.4.2 Horizontal Sync Pulse Width (HSW)                               | . 11 | 1–3 | 33 |

| 11.7.4.3 End-of-Line Pixel Clock Wait Count (ELW)                        | .11  | 1–: | 33 |

| 11.7.4.4 Beginning-of-Line Pixel Clock Wait Count (BLW)                  |      |     |    |

| 11.7.5 LCD Controller Control Register 2                                 |      |     |    |

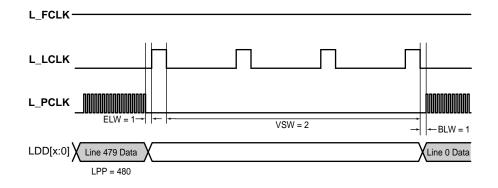

| 11.7.5.1 Lines Per Panel (LPP)                                           | . 11 | 1—: | 35 |

| 11.7.5.2 Vertical Sync Pulse Width (VSW)                                 | . 11 | 1–3 | 35 |

| 11.7.5.3 End-of-Frame Line Clock Wait Count (EFW)                        | .11  | 1—: | 36 |

| 11.7.5.4 Beginning-of-Frame Line Clock Wait Count (BFW)                  | . 11 | 1–: | 36 |

| 11.7.6 LCD Controller Control Register 3                                 | . 11 | 1—: | 38 |

| 11.7.6.1 Pixel Clock Divider (PCD)                                       | .11  | 1_: | 38 |

| 11.7.6.2 AC Bias Pin Frequency (ACB)                                     | . 11 | 1—: | 38 |

| 11.7.6.3 AC Bias Pin Transitions Per Interrupt (API)                     | .11  | 1—: | 39 |

| 11.7.6.4 Vertical Sync Polarity (VSP)                                    | . 11 | 1—: | 39 |

| 11.7.6.5 Horizontal Sync Polarity (HSP)                                  |      |     |    |

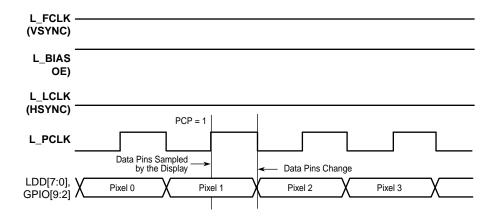

| 11.7.6.6 Pixel Clock Polarity (PCP)                                      | .11  | 1–3 | 39 |

| 11.7.6.7 Output Enable Polarity (OEP)                                    | . 11 | 1-  | 40 |

| 11.7.7 LCD Controller DMA Registers                                      | . 11 | 1—  | 41 |

| 11.7.8 DMA Channel 1 Base Address Register                               | . 11 | 1—  | 42 |

| 11.7.9 DMA Channel 1 Current Address Register                            |      |     |    |

| 11.7.10 DMA Channel 2 Base and Current Address Registers                 |      |     |    |

| 11.7.11 LCD Controller Status Register                                   |      |     |    |

| 11.7.11.1 LCD Disable Done Flag (LDD) (read/write, maskable interrupt)   |      |     |    |

| 11.7.11.2 Base Address Update Flag (BAU) (read-only, maskable interrupt) |      |     |    |

| 11.7.11.3 Bus Error Status (BER) (read/write, maskable interrupt)        |      |     |    |

| 11.7.11.4 AC Bias Count Status (ABC) (read/write, nonmaskable interrupt) |      |     |    |

| 11.7.11.5 Input FIFO Overrun Lower Panel Status (IOL) (read/write,       | •••  | •   |    |

| maskable interrupt)                                                      | . 11 | 1—4 | 46 |

| 11.7.11.6 Input FIFO Underrun Lower Panel Status (IUL) (read/write,      |      | -   |    |

| maskable interrupt)                                                      | . 11 | 1—  | 46 |

| 11.7.11.7 Input FIFO Overrun Upper Panel Status (IOU) (read/write,       |      |     |    |

| maskable interrupt)                                                      | . 11 | 1—  | 46 |

| 11.7.11.8 Input FIFO Underrun Upper Panel Status (IUU) (read/write,      |      |     |    |

| maskable interrupt)                                                      | . 11 | 1—  | 46 |